## END SEMESTER EXAMINATION, NOVEMBER-2018

Semester - 5th

Subject Code: CAI-505

## MICROPROCESSORS AND APPLICATIONS

Full Marks - 70

Time - Three hours

figures in the margin for the questions. indicate full marks

## Instructions:

- All questions of PART-A are compulsory

- Answer any five questions from PART-

in the blanks: Marks - 25 PART -A 1×10=10

FI

- (a) independent of a given computer. is a programming language that is

- 9 A group of 8 bits is called

- 6 memory points to a memory location in R/W called STACK

[Turn over

| 64/CAI-505/M&A (2)            | (f) Monitor program is stored in R/W memory. | counter is cleared (it holds 0000H). |                                                           | (b) LIFO stack is used in 8085.  (c) An instruction has two parts. | (a) The LXI is a two byte instruction. | 2. Write true or false: 1×10=10 | (j) The data bus width of the first Intel Microprocessor (4004) is |                | (i) Microprocessor always recognize first byte as | (h) is the largest positive integer that can be processed by 8085 at one time. |                                              | (g) The numbers of registers and memory cells in a 1024 × 8 memory chip are and | (f) The general purpose registers of 8085 are                                                    | 128 combinations.                             | address 8 K                                | (d) address lines are required to           |

|-------------------------------|----------------------------------------------|--------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------|---------------------------------|--------------------------------------------------------------------|----------------|---------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------|---------------------------------------------|

| 64/CAI-505/M&A (3) [Turn over | (iii) both (i) and (ii) (iv) None of these   |                                      | (c) Counter and time delays can be designed in 8085 using | (iv) a set of memory locations in R/W memory                       | (iii) both (i) and (ii)                | (ii) a 16 bit register          | (i) an 8 bit register                                              | (b) A stack is | (iii) RST 6.5 (iv) RST 5.5                        | (i) INTR (ii) TRAP                                                             | (a) Which interrupt has the lowest priority? | 3. Choose the correct answer: 1×5=5                                             | <ul> <li>(j) Demultiplexing of lower order address bus is<br/>done by the ALE signal.</li> </ul> | (i) JMP is an unconditional jump instruction. | (h) JNC is a conditional jump instruction. | (g) XRI is an example of logical operation. |

- 0 In 8085, register pairs are obtained by combining

- (i) 8 bit registers

- (ii) Accumulator and Flag

- (iii) Accumulator and Memory

(iv) Stack

- Which of the following is an example of data transfer instruction?

- (i) STA 16-bit

- (ii) ADD M

(iii) RLC

(iv) RST 1

PART-B

(a) What is a microprocessor? microcontroller. difference between microprocessor Marks - 45 Explain the and

4.

(b) Define the terms : bit, word and instruction.

S. (a) Define the term Flag and explain how the different flags of 8085 are affected

9 Classify the instructions in terms of their word size and give suitable examples of each.

4

64/CAI-505/M&A

- (a) Name the five major groups of 8085 instructions with examples.

- Specify the opcode, operand and meaning of the following instructions:

- (i) MOV M, D

(ii) ADD B

(a) If the starting address of the following program. program is 3050H, then assemble

MOV B, C MVI C, DFH

LDA E200H

SUB B

ANI IIH at mining control of A STA E300H

RST I

(b) Write an ALP to subtract two bytes already the second byte 23H from the first byte 49H stored in memory locations C051H and and store the answer in memory location location C052H holds the byte 23H. Subtract C052H. Location C051H holds 49H and DDDOH.

64/CAI-505/M&A

(5)

Turn over

- 8. (a) Design a 4-bit register (4 input lines and 4 output lines) to store 4-bits using latches.

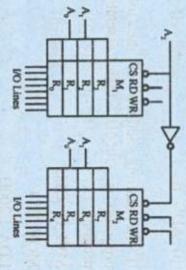

- (b) For the two memory chips (M1 and M2) shown in the figure below, identify the memory address range.

- 9. (a) The memory address of the last location of a 1K byte memory chip is given as FBFFH.Specify the starting address.

- (b) Explain the function of ALE and IO/M signals of 8085.

- (c) If the 8085 has fetched the m/c code located at the memory location DFFFH, specify the contents of program counter.

- (a) Make a comparison between memory mapped I/O and I/O mapped I/O interfacing schemes.

- (b) Identify the machine cycles in the following instructions:

- \* SUB B

- \* ADI 55H

- \* STA E123H

- 11. (a) If 8085 adds 87H and 79H, specify the contents of accumulator and the status of sign, zero and carry flag.

- (b) Draw the timing diagram of MVI A, 55H instruction.

110(B)

3